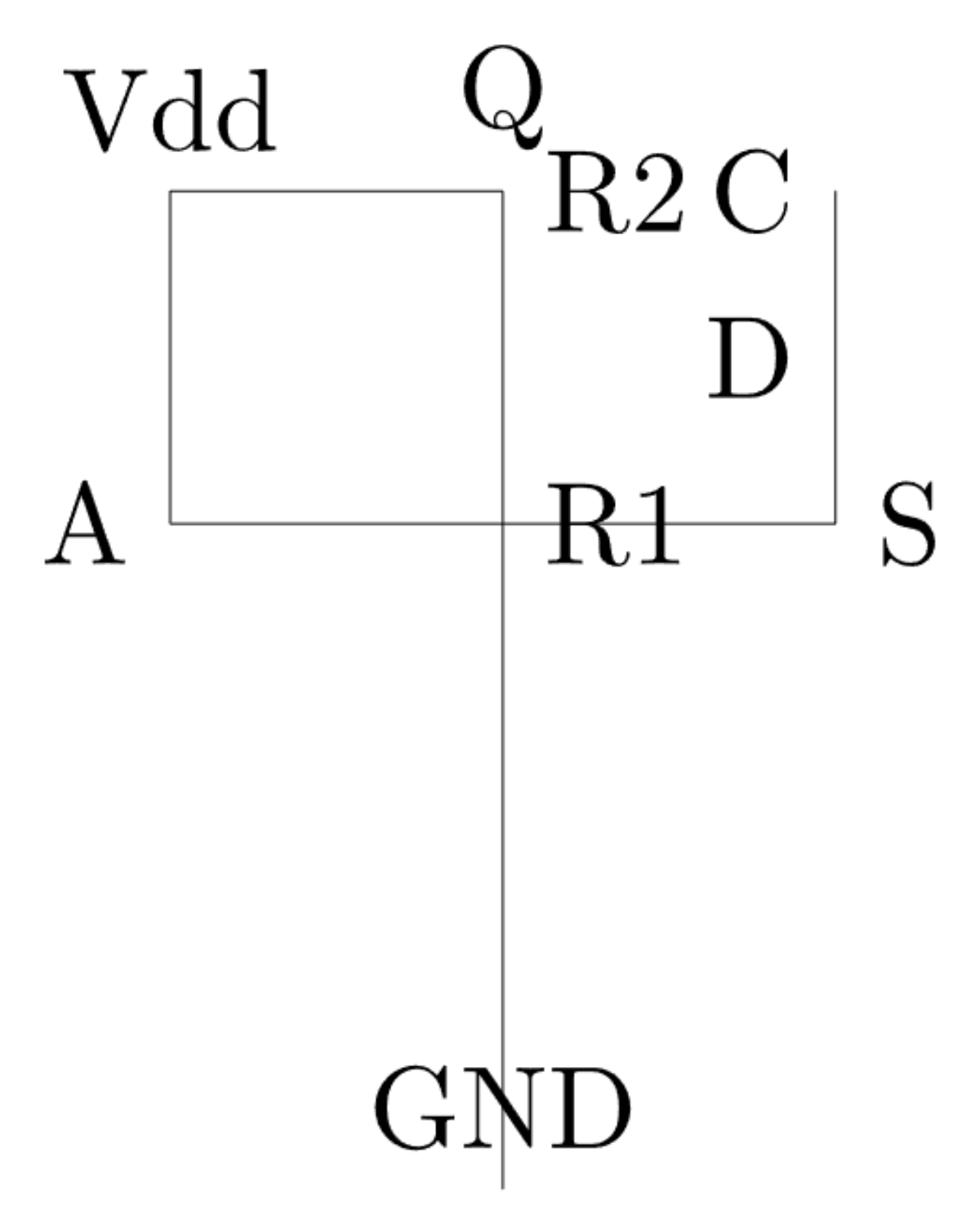

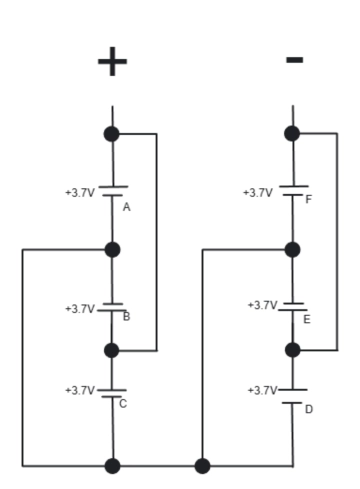

Free Binary RAM Cell

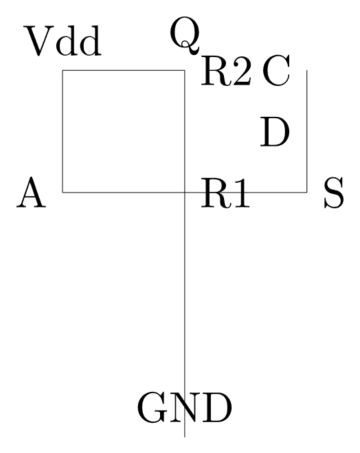

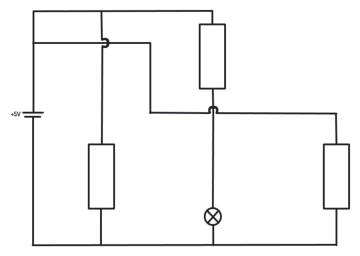

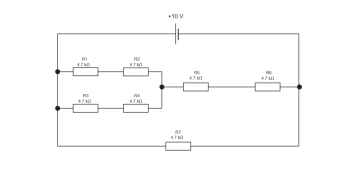

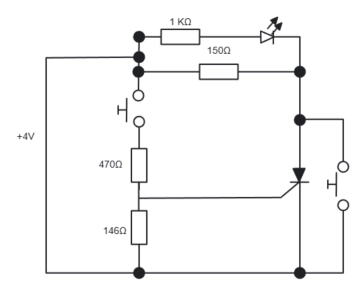

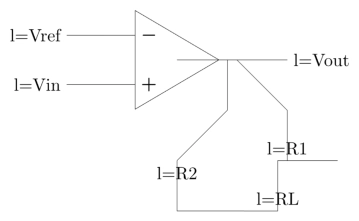

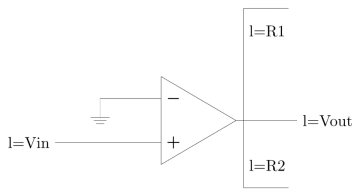

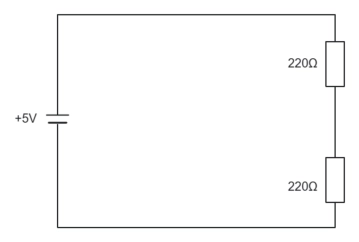

The Binary RAM Cell template is a professional engineering tool designed to facilitate the clear visualization and architectural documentation of a single-bit memory storage element. This resource is ideal for digital logic designers, computer architects, and semiconductor engineering teams who require a standardized schematic for mapping out volatile data storage structures. Users begin the workflow by establishing the primary voltage supply, labeled Vdd, and the common ground reference to define the cell's power boundaries. They then move through a step-by-step process of configuring the selection and data lines, utilizing control points like R1, R2, and S to manage the read and write states of the bit. Completing this logical process results in a high-fidelity technical roadmap that enables stakeholders to achieve accurate hardware validation and verified memory addressing performance.